[Sequential Logic Circuit] 래치(Latch)

해당 강의노트는 S. Brown and Z. Vranesic, McGraw-Hill의 [Fundamentals of Digital Logic with VHDL Design, 3rd Edition] 책을 기반으로 작성되었습니다

Latch

- Basic Latch

- Gated SR Latch

- Gated D Latch

Basic Latch

래치(Latch)란?

비트를 임시로 저장할 수 있는 기억소자(memory) 중 하나로, 두 개의 게이트(gate)로 구성된다. 게이트 하나의 출력이 다른 게이트의 입력으로 다시 연결되는 피드백(Feedback)형태를 가지고 있다.

SR 래치(SET-RESET Latch)

입력이 S(set)와 R(Reset)로 두개이고, 출력의 형태가 SET, RESET 두 가지인 래치의 한 종류

1. Latch built from NAND gates

active-low로 동작하는 구조로 NAND게이트로 구성

2. Latch built from NOR gates

active-high로 동작하는 구조로 NOR게이트로 구성

SR 래치 동작 예시: active-high

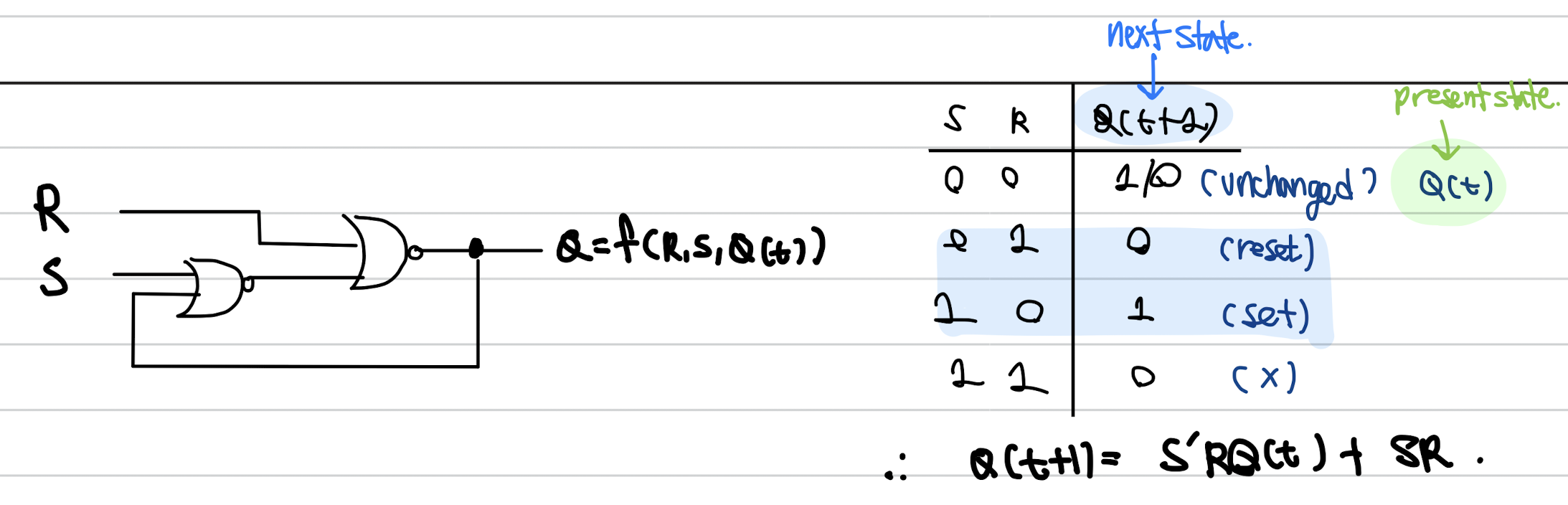

active-high로 동작하는 SR latch를 살펴보자. 이는 아래와 같이 두 입력이 모두 거짓(0)일때만 참(1)을 출력하는 NOR게이트로 구성된다.

현재 상태인 Q(t)와 R, S로 다음 상태를 아래와 같이 표현할 수 있다.

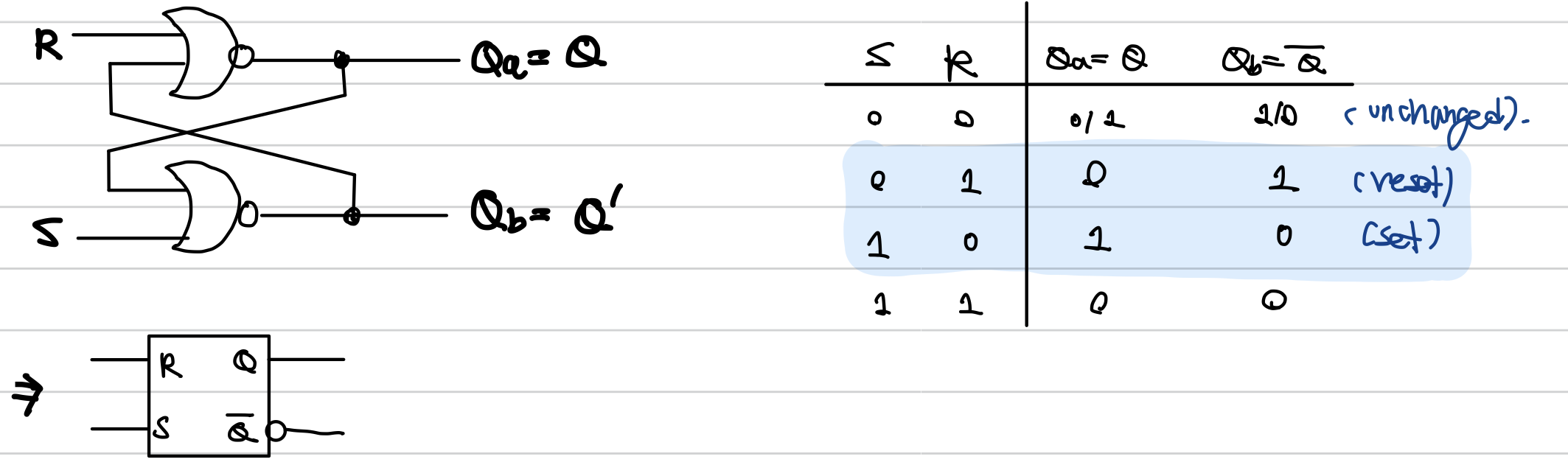

최종적으로 active-high를 가지는 SR 래치를 구현하면 아래와 같이 두 개의 입력(S바, R바)과 두 개의 출력을 가진다.

S,R 값에 따른 래치 상태변화는 다음과 같다. 래치가 정상적으로 동작한다면 Q와 Q'은 반드시 서로 반대되는 출력값을 가진다. 만약 4번의 경우처럼 두 입력 모두 high(1)값을 준다면 Q와 Q'이 서로 보수의 값을 갖지 않고 모두 low(0)의 출력이 되므로 무효 조건(오류)인 경우이다. (하지만 실제로는 게이트의 전파 지연 시간 때문에 어느 하나가 먼저 high가 되면 다른 것은 low가 될 수 밖에 없다. 즉, 전파 지연시간에 따라 출력을 예측할 수 없기 때문에 게이트의 동작에 있어 신뢰성이 없어진다.)

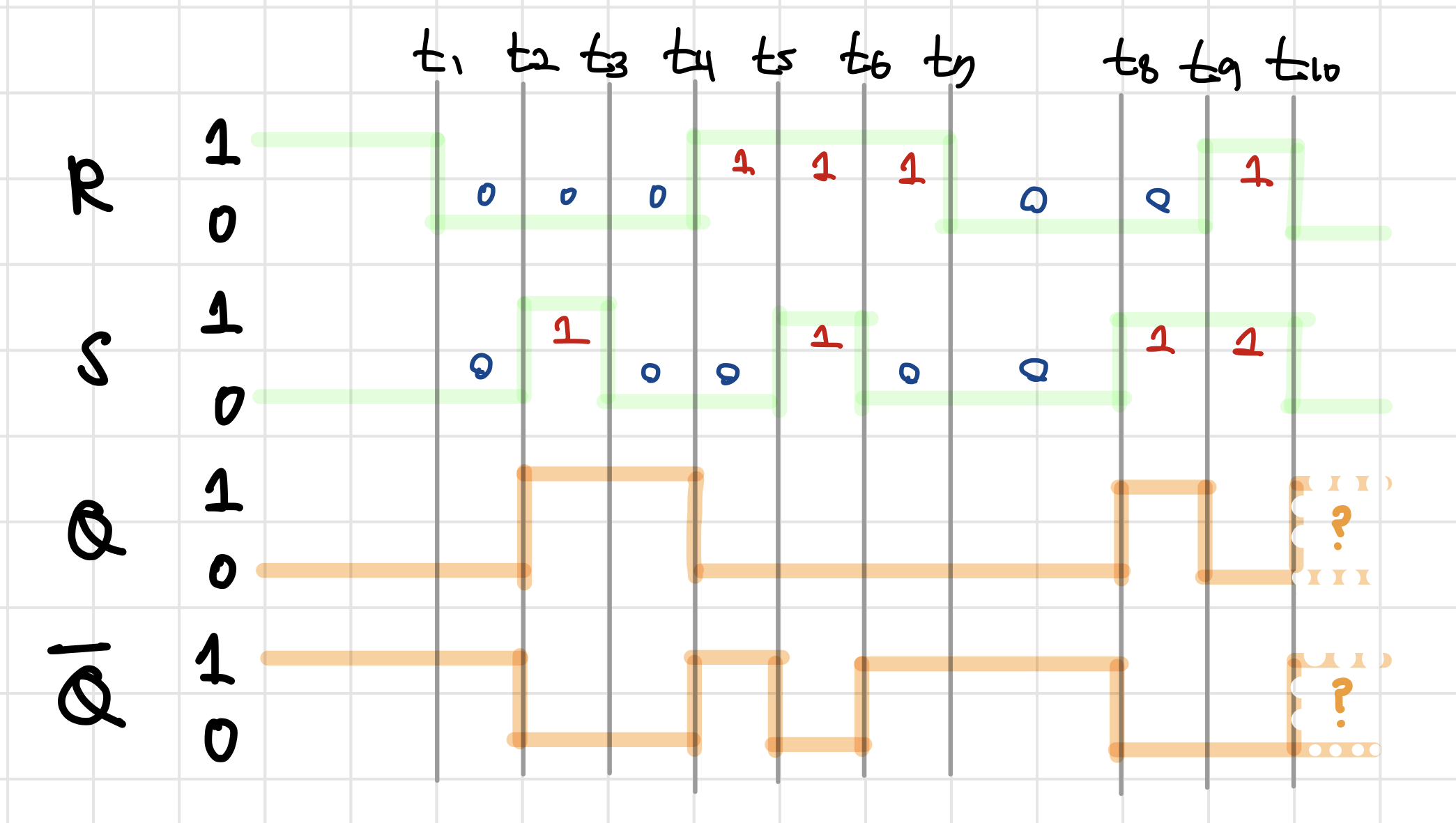

시간에 따른 Q, Q'의 타이밍 다이어그램은 다음과 같다.

Gated SR Latch

SR 래치의 문제점

문제점1. 기존의 SR 래치의 단점인 S와 R을 동시에 1/0으로 만든다면 NOR/NAND의 특성 때문에 출력이 모두 0/1이 된다는 점

문제점2. 노이즈가 발생해 R, S 신호를 교란해 기대하지 않은 결과가 나오는 것을 방지하지 못함

제어장치가 있는 SR 래치(Gated SR Latch with NOR gates)

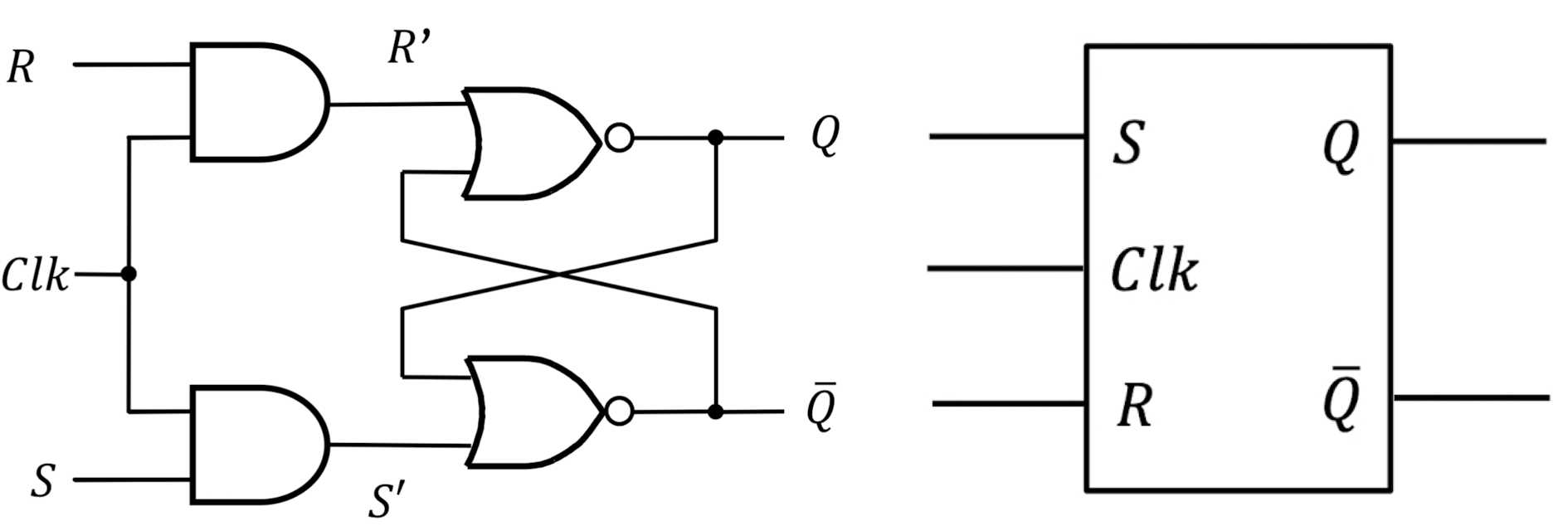

Clk(clock) 신호를 추가해 문제점2를 해결할 수 있다. Clk를 추가한 Gated SR 래치는 다음과 같다

Clk가 0인 경우: 현재 상태 유지(no change)

- NOR 게이트에 0, x가 들어올 경우 항상 x'이 출력(입력이 x 하나인 NOT gate와 같아짐)

- 즉 clk가 0인 경우, S와 R값의 상관 없이 아래의 그림처럼 현재 상태를 유지하게 됨

Clk가 1인 경우

- 기존의 래치와 똑같은 역할을 수행

- 즉 R이나 S로 값을 바꿔줄 때만 Clk를 1로 만들어 수정가능하고, 그렇지 않을 때는 0으로 만들어 수정을 못하게 막음

- 이 경우 기존의 SR 래치의 문제점 중 노이즈가 값을 뒤집어버리는 경우는 해결할 수 있음

- 단, S와 R이 동시에 1이 되는 문제는 해결하지 못함

Gated D Latch

Gated SR 래치의 문제점

문제점1. 기존의 SR 래치의 단점인 S와 R을 동시에 1/0으로 만든다면 NOR/NAND의 특성 때문에 출력이 모두 0/1이 된다는 점

문제점2 -> 해결

제어장치가 있는 D 래치(Gated D Latch with NAND Gate)

Gated SR래치와 다르게 S와 R이 항상 반대의 값을 가지게 R에 S의 NOT을 입력하는 방법을 이용해보자.

*NAND gate는 두 입력이 모두 참(1)일 때만 출력값이 거짓(0)

Clk가 0인 경우: 현재 상태 유지(no change)

- NAND 게이트에 1, s가 들어올 경우 항상 s'이 출력(입력이 x 하나인 NOT gate와 같아짐)

- 즉 clk가 0인 경우, D값의 상관 없이 아래의 그림처럼 현재 상태를 유지하게 됨

Clk가 1인 경우

- D가 0이면 Q가 1로, D가 1이면 Q가 1로 설정됨

- 이렇듯 D입력으로 들어가는 값이 그래도 Q에 반영되므로 D 래치라고 함.

- D의 값이 S로, D의 NOT값이 R로 들어가기 때문에 S와 R이 동시에 1이 되는 상황 불가 -> 문제점2 해결